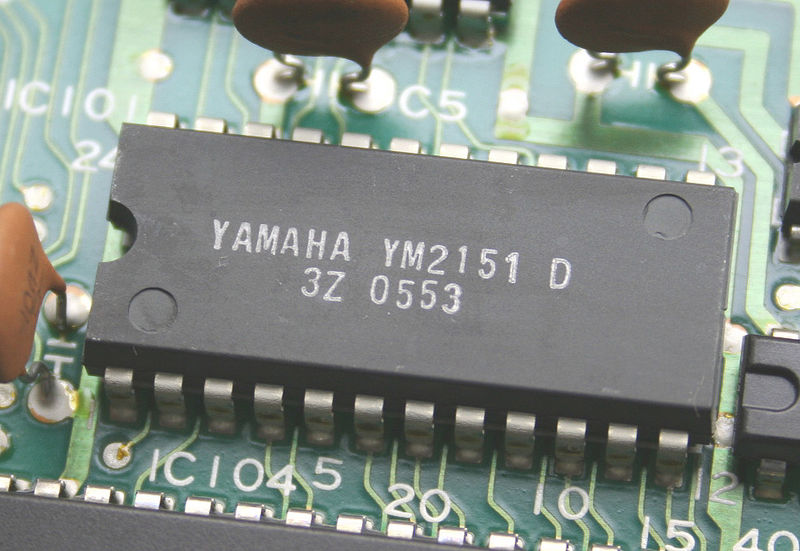

| 初期のYM2151 シボ(皺、表面荒さ加工)がなく、捺印文字もシンプル |

中期のYM2151 皺あり |

|

| 端子番号 | 端子名称(仮名称) | I/O | 端子機能 |

| 1 | VSS (GND) |

- | 0V端子 |

| 2 | iRQ | Interrupt ReQuest 割込み要求出力端子。内蔵タイマー2つのうちどちらかのキャリーアウトによりLowレベルとなる。 | |

| 3 | IC | I | Initial Clear RESET信号入力端子 |

| 4 | A0 | I | Address0 アドレス選択信号入力 |

| 5 | WR | I | Write ライト信号入力 |

| 6 | RD | I | Read リード信号入力 |

| 7 | CS | I | Chip Select チップセレクト信号入力 |

| 8 | CT2 | O | ConTrol2 外部機器のコントロールを行う。初期状態はLowレベル。 |

| 9 | CT1 | O | ConTrol1 外部機器のコントロールを行う。初期状態はLowレベル。 |

| 10 | D0 | I/O | Data BusD0 3ステートデータバス |

| 11 | VSS (GND) |

- | 0V基準電圧端子 |

| 12 | D1 | I/O | Data BusD1 3ステートデータバス |

| 13 | D2 | I/O | Data BusD2 3ステートデータバス |

| 14 | D3 | I/O | Data BusD3 3ステートデータバス |

| 15 | D4 | I/O | Data BusD4 3ステートデータバス |

| 16 | D5 | I/O | Data BusD5 3ステートデータバス |

| 17 | D6 | I/O | Data BusD6 3ステートデータバス |

| 18 | D7 | I/O | Data BusD7 3ステートデータバス |

| 19 | SH2 | - | Sample and Hold2 |

| 20 | SH1 | - | Sample and Hold1 |

| 21 | SO | - | Serial Output |

| 22 | VDD (+5V) |

- | +5V電源入力端子 |

| 23 | φ1 | O | Clock for D/A D/Aコンバータ用クロック出力端子および各種同期信号基準。 φ1のネガティブエッジをトリガーとして、iRQ,CT1,CT2,TO(内部接続のコントロール信号、外部には出力されていない),SH1,SH2,SOの状態が変化する。 |

| 24 | φM | I | System Clock システムクロック入力端子。内部で2分周し使用される。発音の基準周波数。 |

| ページ | 誤 | 正 |

| 2 | ■ブロックダイヤグラム EGユニット中のEG(SIRIAL) |

EG(SERIAL) |

| 2 | ■ブロックダイヤグラム ACCユニット中のDO(SIRIAL) |

Do(SERIAL) |

| 2 | ■ブロックダイヤグラム IRQ |

iRQ |

| 3 | ●アドレスマップ(1);WRITE MORE | WRITE MODE |

| 5 | ●CONECTION=(FS) | CONNECTION=(FS) |

| 9 | ■ピン機能 ●D0~D7 …マルチプレソクス双方向性 |

マルチプレクス双方向性 |

| 10 | Vss:Grand(input) | Ground(input) |

| 11 | 7.〔IRQ〕 | iRQ |

| 12 | 10.〔IRQ、〕 | iRQ、 |

| 12 | ●READ TIMING OPM <注>TDS、TDHNは |

TDS、TDHWは |

| 12 | ●READ TIMING Aφ |

A0 |

| 13 | ●SYSTEM BLOCK DIAGRAM OPM (YM2151) SAMPL & MOLD |

SAMPLE & HOLD |

| 14 | ●DAC INTERFACE OPM (YM2151) iC 3 |

IC 3 |